팹리스와 파운드리, 반도체 생태계 이야기

세 줄 요약

- 반도체 IP는 신지식재산권에 속하는 권리로 칩 설계의 효율화를 위해서 태어났다.

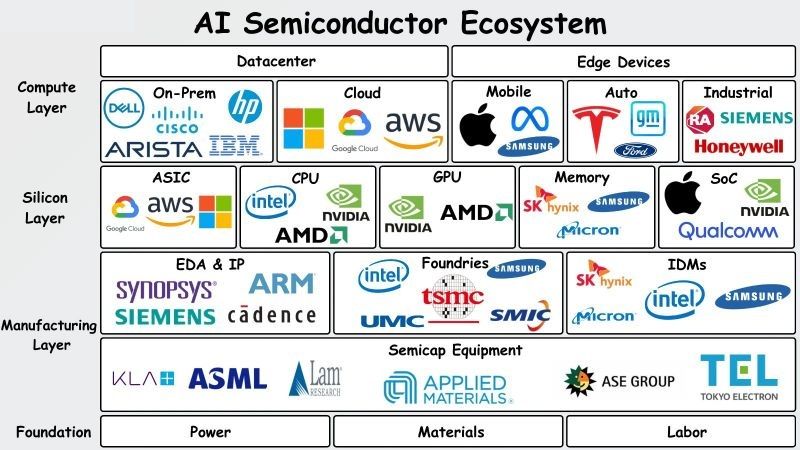

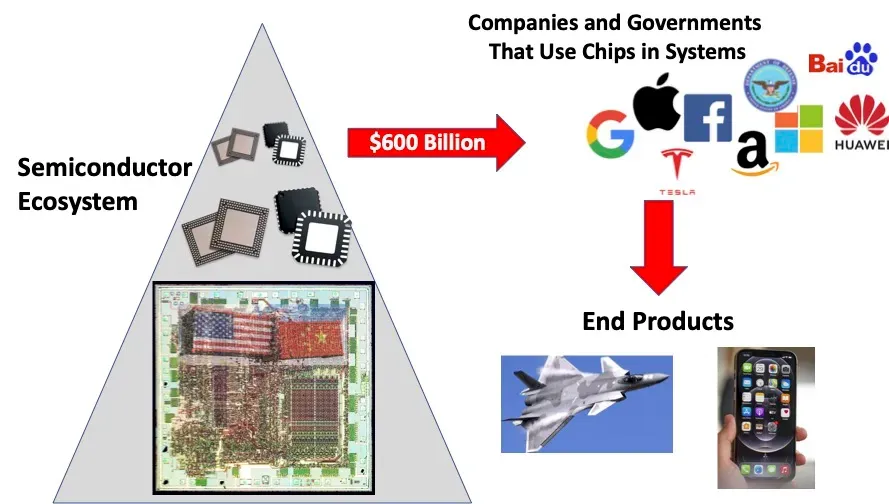

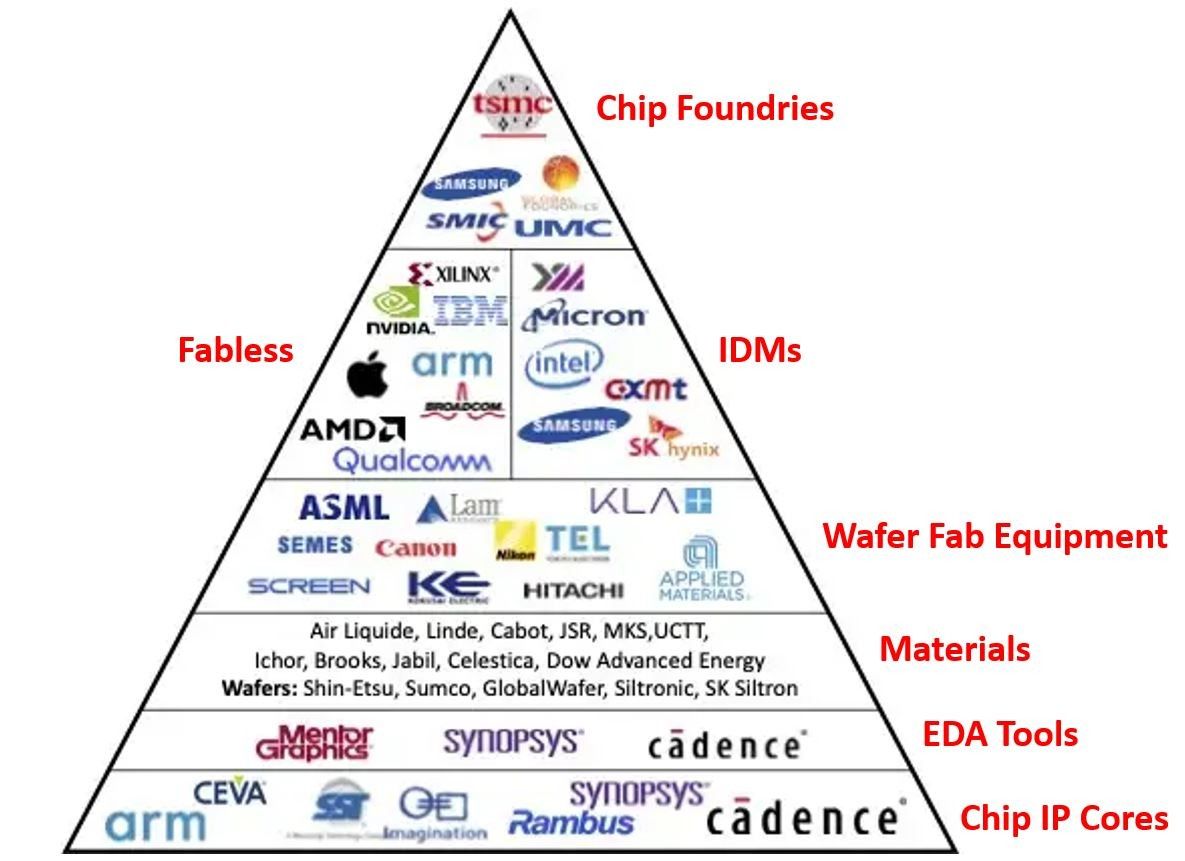

- 반도체 생태계는 팹리스, 파운드리, IDM 등 여러 분야로 구성됐으며, 반도체 IP 기업은 생태계의 뿌리에 해당한다.

- 반도체 IP 이용의 장점은 비용절감, 시간절약, 최적화와 확장성, 위험 감소, 경쟁력 향상 등 다양하다.

반도체 IP의 탄생

‘지식재산권’이라는 말을 들어본 적이 있는가? 얼마 전까지 ‘지적재산권’이라고 불렸던 지식재산권은 “법령 또는 조약 등에 따라 인정되거나 보호되는 지식재산에 관한 권리”(지식재산기본법 제3조 3항)를 말한다. 여기서 ‘지식재산’은 인간의 창조적 활동 또는 경험 등에 의하여 창출되거나 발견된 지식, 정보, 기술, 사상이나 감정의 표현, 영업이나 물건의 표시, 생물의 품종이나 유전자원(遺傳資源), 그 밖에 무형적인 것으로서 재산적 가치가 실현될 수 있는 것을 가리키는데(지식재산기본법 3조 1항), 간단히 말하면 ‘인간에 의해 발생한 유형, 무형의 재산적 권리를 의미한다.

보통 IP(Intellectual Property Rights, IP 또는 IPR)라 불리는 지식재산권은 특허법, 실용신안법, 상표법, 디자인보호법 등을 다루는 산업재산권, 문화예술 분야의 저작권법, 사회/기술 변화에 따른 새로운 형태의 신지식재산권 등 3가지 분야로 나눌 수 있는데, 오늘 이야기할 반도체 IP는 신지식재산권에 속한다.

보통 반도체 산업에서 IP라 하면, 특정 기능을 수행하기 위해 설계된, 재이용 가능한 반도체 설계 블록을 의미한다. 회로처럼 우리가 단번에 이해하기 쉬운 부분은 물론이고, 칩 레이아웃 디자인, SoC(System on Chip) 또는 FPGA(Field Programmable Gate Array) 회로 설계 시 마이크로프로세서, 메모리, 디지털 신호 처리기, 아날로그 신호 처리기, 다양한 입출력(I/O) 회로 등 매우 다양한 부분이 반도체 설계 블록에 포함된다.

반도체 IP가 탄생한 이유는 칩 설계의 효율화를 위해서인데, 반도체 디자이너가 이를 활용함으로써 반도체 칩을 빠르게 개발하도록 돕는다. SoC처럼 복잡한 반도체 제품 개발에 널리 사용되고 있다.

반도체 IP 개념이 생기기 전에는

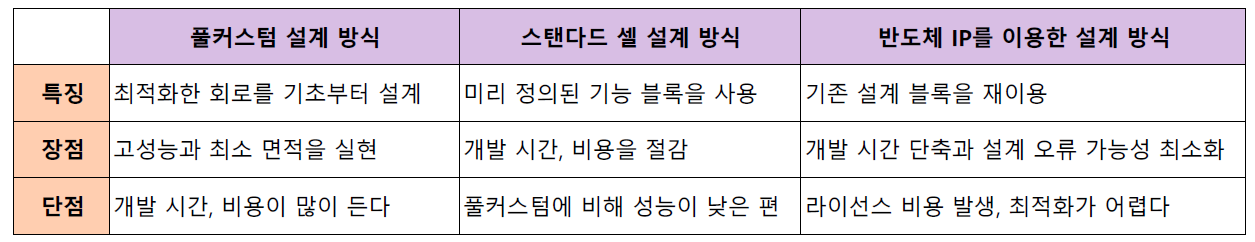

과거 반도체 IP라는 개념이 생겨나기 전에는 풀커스텀 설계나 스탠다드 셀 설계 방식으로 반도체를 설계했다.

풀커스텀 설계는 회로나 레이아웃을 특정 애플리케이션이나 요구 성능에 정확하게 들어맞도록 기초부터 설계하는 방법으로, 제로에서 작업을 시작하는 것이라 설계 유연성이 높고 최적화가 가능해 고성능, 소비 전력 절감 등 특정 목표를 달성하기 위해 사용하던 방법이다. 다만 시간과 비용이 많이 소모된다.

한편, 스탠다드 셀 설계는 미리 정의된 기능 블록(스탠다드 셀)을 조합해 반도체를 설계하는 방법이다. 설계 공정이 효율화되고 개발 시간과 비용을 줄일 수 있지만, 풀커스텀 방식과 비교하면 최적화에 한계가 있다는 단점이 있다.

어쨌거나 이들 방식은 둘 다 제로부터 시작해야 했고, 재이용할 수 있는 콤포넌트는 한정적이었다. 따라서 설계에 많은 시간이 필요했고, 이로 인해 납기와 비용이 늘어난다는 문제를 피할 수 없었다.

반도체 IP를 이용하면 설계 공정의 초기 단계부터 높은 수준으로 최적화된 콤포넌트를 이용할 수 있어서 설계부터 제품화까지 시간을 크게 줄일 수 있다. 그리고 IP를 재이용함으로써 새로운 설계에 들어가는 비용을 낮추고, 연구 개발이나 검증 과정에 필요한 투자를 줄일 수도 있다. 여기에 더해 이미 시장에서 검증된, 널리 채용하고 있는 IP를 사용하는 것이라 설계 오류나 성능상 문제가 생길 위험도 크게 낮출 수 있다.

반도체 생태계의 구성원

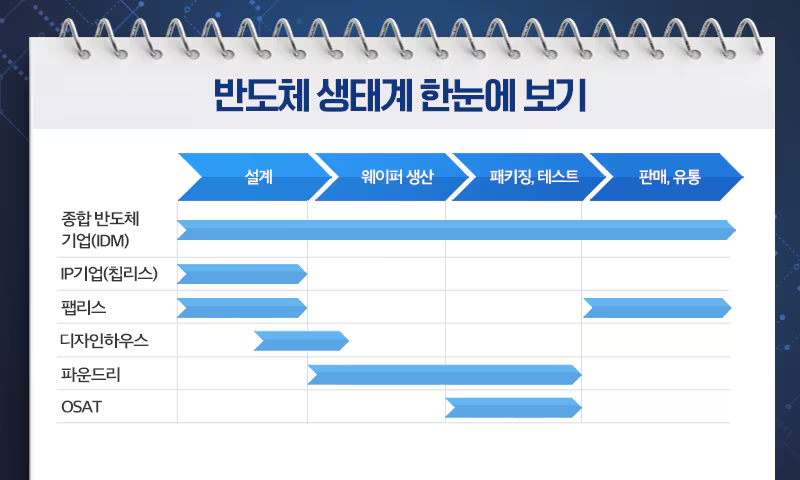

반도체 업계는 원래 IDM(Integrated Device Manufacturer, 종합 반도체 기업)이라 불리는, 반도체의 설계부터 제조까지 모두 맡아서 진행하는 제조사를 중심으로 움직였는데, 칩 구성이 복잡해지고 공정의 미세화가 진행되면서 현재는 분업이 활발히 진행되고 있다.

분업은 ①팹리스(Fabless)라 불리는, 자기 회사에서 반도체를 생산하지(Fabrication) 않고(less) 반도체 설계에만 집중하는 회사가 칩을 설계하고, ②파운드리(Foundry)는 팹리스로부터 제조를 위탁받아 생산한 다음, ③OSAT(Outsourced Semiconductor Assembly and Test, 반도체 조립 & 검수 외주사)가 생산된 반도체를 패키징하고 테스트하는 형식으로 진행된다.

반도체 생태계 분업화는 크게 보면 팹리스, 파운드리, OSAT으로 나눌 수 있지만, 더 세분화하면 디자인 하우스, IP 기업 등 더 자세히 나눌 수 있다. 디자인 하우스는 팹리스 기업이 설계한 제품을 각 파운드리 생산공정에 적합하도록 최적화된 디자인 서비스를 제공하고, IP 기업은 특정 설계 블록을 팹리스나 IDM, 파운드리 등에 제공하고 IP 사용에 따른 라이선스료를 받는다.

우리가 잘 아는 GPU 제조사 엔비디아가 팹리스에 해당하고, 세계의 반도체 공장이라 불리는 TSMC가 대표적인 파운드리이며, 대만의 ASE나 우리나라의 하나마이크론 등은 OSAT 업체다. 삼성전자는 팹리스, 파운드리, OSAT를 모두 수행하기 때문에 앞서 설명한 IDM이라 할 수 있다. 반도체 IP는 주로 팹리스가 칩을 설계할 때 이용한다.

반도체 IP를 이용하는 이유

팹리스 회사는 다음과 같은 이유로 반도체 IP를 이용한다.

장점 1. 비용을 줄일 수 있다.

기초 설계부터 시작하지 않고 기존 IP를 라이선스받아서 이용하면 연구, 개발 비용을 줄일 수 있다. 또한, 반도체 IP를 이용하면 설계 과정에서 생기는 오류를 원천적으로 방지할 수 있어서 오류로 인한 재설계 과정도 피할 수 있다. 이는 개발 비용의 전체적인 절감으로 이어진다.

장점 2. 개발 기간을 단축할 수 있다.

반도체 IP를 이용하면 팹리스 기업은 설계 과정을 신속하게 진행할 수 있다. 선행 디자인된, 이미 검증을 마친 IP 코어를 조합하면 설계부터 시제품 제작, 제품화까지 걸리는 시간을 단축할 수 있으므로 시장 투입까지 시간을 크게 줄일 수 있다.

보통 IP를 직접 개발하고 검증하려면 약 24개월~30개월 정도 시간이 걸린다고 하고, 반도체 새로운 칩을 직접 개발하고 양산까지 도달하려면 약 42개월~60개월이 걸린다고 한다. 팹리스가 IP를 개발하지 않고 IP 제공사로부터 라이선스받으면 IP에 들어가는 시간을 줄일 수 있어, 약 18개월~30개월이면 새로운 칩을 양산할 수 있게 되는 것이다.

시간이 얼마나 중요한지는 SK하이닉스와 삼성전자와 차세대 HBM(고대역폭 메모리)을 상대보다 먼저 시장에 내놓기 위해 얼마나 치열하게 경쟁하는지를 보면 알 수 있다. 단 몇 개월을 줄이고자 전사적인 역량을 총동원하는데, 최대 약 30개월을 줄일 수 있다는 건 사용하지 않을 도리가 없는 셈이다.

장점 3. 최적화와 확장성

반도체 IP 대부분은 특정 애플리케이션이나 고객의 요구에 맞춰 최적화가 가능하다. 폭넓은 시장에서 고객사의 다양한 요구에 대응하는 제품을 처음부터 일일이 만들지 않고, 라이선스받은 반도체 IP를 최적화하고 확장함으로써 팹리스 기업은 다양한 제품을 효율적으로 개발할 수 있다.

장점 4. 위험 감소

이미 검증을 마친 IP 코어를 이용한다는 건, 설계 과정에서 생길 수 있는 시행착오를 건너뛸 수 있다는 뜻이다. 신뢰성 높은 IP를 이용하면 설계 실수로 인해 생길 수 있는 시간 지연, 실패의 위험을 피할 수 있게 되고, 이는 최종 제품의 품질과 신뢰성을 높이는 결과로 이어진다.

장점 5. 핵심역량에 집중

특정한 기술 분야, 기능에 특화된 IP를 이용한다는 건, 해당 분야의 전문지식을 팹리스가 그대로 활용할 수 있다는 뜻이다. 이를 통해 팹리스는 다른 곳에 한눈팔지 않고 자사의 핵심역량에 계속해서 집중하면서도, 제품의 성능을 높일 수 있다.

장점 6. 경쟁력 향상

팹리스가 우수한 IP를 사용하면 경쟁력 있는 제품을 시장에 빨리 내놓을 수 있다. 또한, IP를 활용하면 최신 기술 트렌드에 빠르게 대처할 수 있게 되어, 제품의 포트폴리오를 넓게 가져갈 수 있다.