HBM 고성능화의 일등공신, TSV

HBM과 같은 첨단 반도체를 만들기 위해선 수많은 최신 기술이 투입된다. 칩의 일괄제조 아이디어를 패널 레벨에서 제조에 응용한 PLP(Panel level package) 기술, 2개 이상의 반도체 기기의 메탈 패드를 구리 범프 등을 거치지 않고 직접 연결하는 기술인 Hybrid Bonding, 반도체 패키지 안에 상호 연결용 실리콘 기판을 채워 반도체 패키지 위쪽에 탑재되는 실리콘 칩을 고밀도로 탑재하고 서로 연결하는 실리콘 브리지(Silicon Bridge) 기술 등 일일이 열거하자면 그야말로 끝이 없을 정도다.

이런 기술을 모두 픽업해서 다루는 건 사실상 어렵기에 그동안 HBM 등의 첨단 반도체를 만들기 위한 핵심 기술 중 얼개에 해당하는 ‘3차원 집적 기술’과 ‘2.5차원 패키징 기술’에 대해서만 다루어보았다. 자동차를 예로 들면 ‘고효율을 자랑하는 엔진 구조’, ‘즉각적인 반응이 가능한 전자 제어 기술’처럼 자동차에 대해서는 일부이지만, 그 안에 또 여러 세부 기술을 포함하는, 일종의 ‘중간 규모’의 시스템적 특징을 설명한 셈이다.

[HBM을 위한 핵심 반도체 기술, 3차원 집적 기술] 기사 보러 가기

[HBM 고성능화를 위한 핵심 기술, 2.5차원 패키징 기술] 기사 보러가기

이번 시간에는 ‘중간 규모’의 시스템적 특징이 아니라 PLP, 하이브리드 본딩처럼 첨단 반도체에 적용되는 구체적인 기술 중 하나인 ‘TSV’를 살펴보고자 한다. 왜 예외적으로 ‘중간 규모’의 시스템적 특징이 아니라 구체적인 기술을 설명하게 됐냐면, ‘TSV’ 기술은 자동차로 따지면 ‘내연기관’처럼 HBM에 있어서 그야말로 핵심적인 기술이기 때문이다.

세 줄 요약

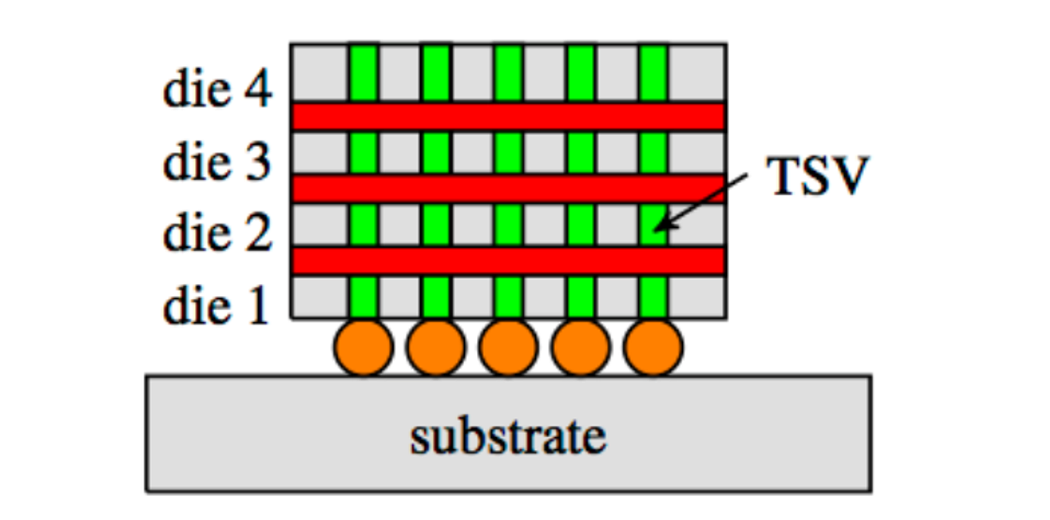

- TSV는 실리콘 관통 전극의 약자로 수직으로 쌓은 칩을 서로 연결해주는 신경망 같은 존재다.

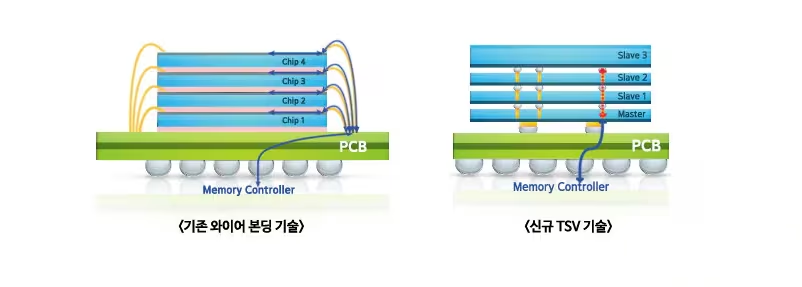

- 기존 방식인 와이어 본딩과 비교해 처리 속도 고속화, 소형화와 고밀도화, 소비 전력 절감 등이 장점이다.

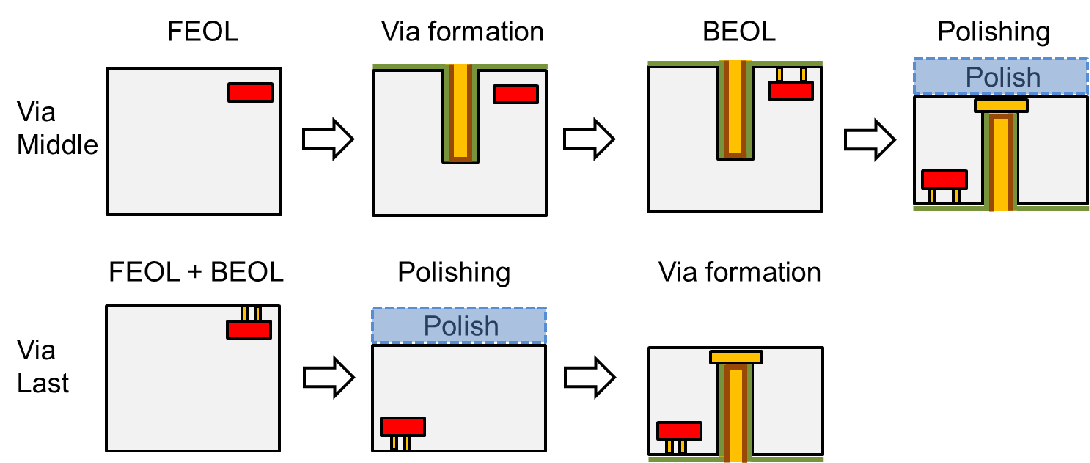

- TSV의 구멍(via)을 언제 만드느냐에 따라 via middle, via last 공정으로 나눌 수 있으며 반도체 제작 공정 중 전자는 전공정, 후자는 후공정에 속한다.

고성능 반도체를 위한 핵심 기술, TSV

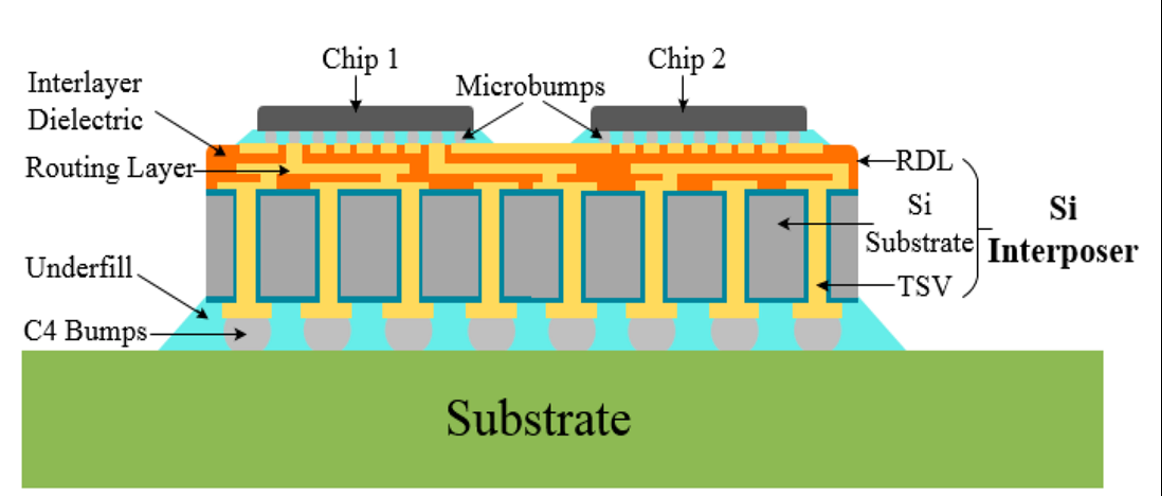

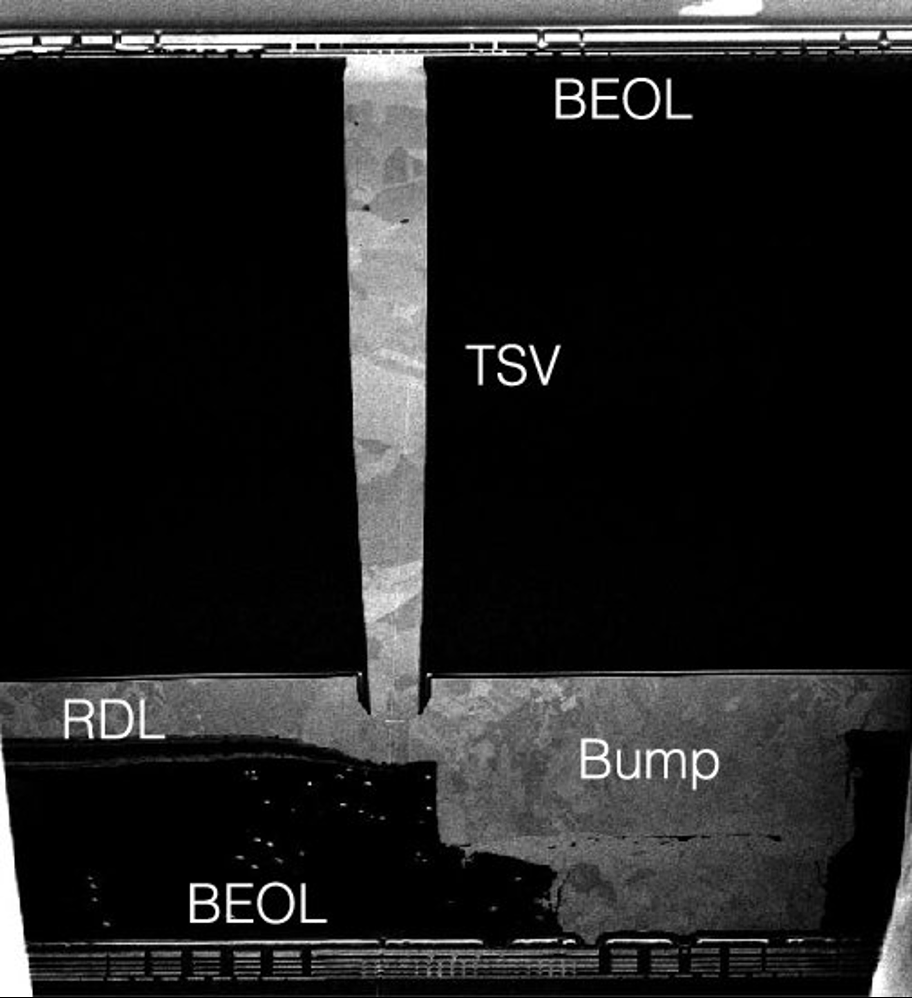

TSV는 ‘Through silicon via’의 약자로 ‘실리콘 관통 전극’이라 번역할 수 있다. 기존에는 구리 와이어를 이용해 칩을 전기적으로 연결했는데, TSV는 실리콘 웨이퍼 내부에 위아래로 관통하는 가는 구멍(via)을 뚫고 그 안쪽에 금속을 채워 넣어 전극을 만든 후, 마이크로 범프를 통해 실리콘 칩을 전기적, 그리고 기계적으로 연결하는 기술이다. 층층이 쌓은 칩을 서로 이어주기 때문에 고층 빌딩 사이를 빠르게 왕래하게 만들어주는 엘리베이터와 비슷한 개념이라고 설명하기도 한다.

TSV의 첫 번째 장점은 처리 속도를 고속화할 수 있다는 점이다. TSV를 이용하면 와이어 본딩과 비교해 칩 사이의 거리를 단축할 수 있는데, 이는 신호를 더 빠르게 전달할 수 있다는 뜻이다. 그리고 단자가 많아져도 쉽게 대응할 수 있다.

두 번째 장점은 소형화, 고밀도화가 가능한 점을 꼽을 수 있다. 여러 칩을 수직으로 쌓은 후 TSV 기술을 이용해 이 칩들을 서로 연결해주면 하나의 칩처럼 작동하게 할 수 있다. 즉, 고밀도화가 가능하다. 또한, 이 방법은 와이어 본딩을 이용했을 때와 비교해 옆으로 튀어나오는 와이어가 없어지므로 면적을 줄이는 효과도 거둘 수 있다. 소형화가 가능한 것이다.

세 번째는 소비 전력 절감이다. TSV를 이용하면 신호 전달 거리가 줄어들기 때문에 배선 저항도 자연스럽게 줄어들고, 이는 소비 전력 절감으로 이어진다.

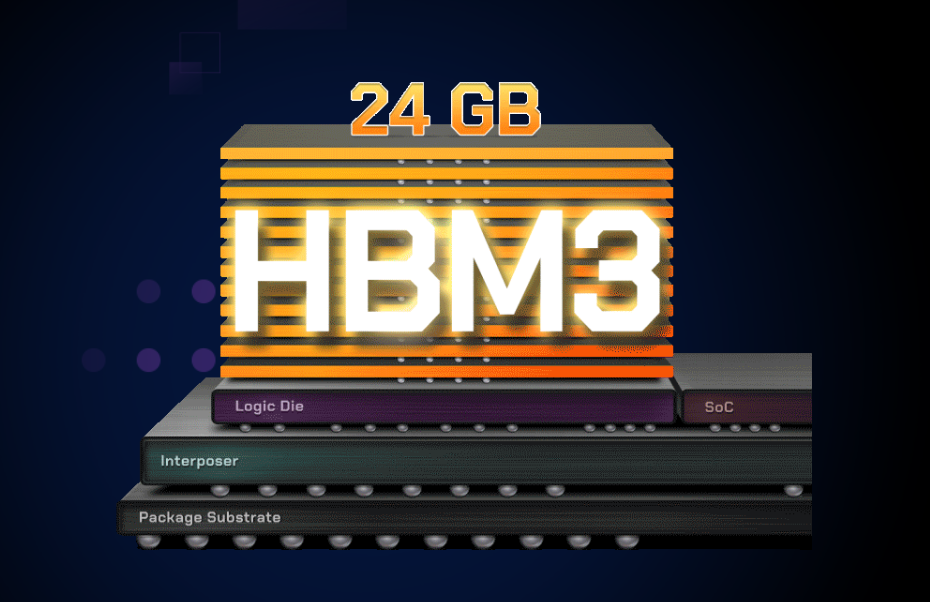

TSV 기술은 지금 HBM(High band width memory, 고대역폭 메모리)를 비롯해 적층형 이미지 센서, 실리콘 인터포저 등에서 적극적으로 이용되고 있다. 우리나라에서는 삼성전자가 2010년에 세계 최초로 TSV 기술을 적용한 D램 모듈을 개발했고, 2014년에는 역시 세계 최초로 3차원 TSV 적층 기술을 이용해 64GB DDR4 서버용 D램 모듈 양산을 발표했다. 이 TSV 기술은 앞으로도 서로 다른 칩을 수직으로 연결함으로써 첨단 반도체의 성능을 높이는 핵심 기술로 많은 기대를 모으고 있다.

TSV는 어떻게 만드나?

TSV의 via를 만드는 방법에는 여러 종류가 있는데, 요즘은 대부분 비아 미들 공정(via middle process)과 비아 라스트 공정(via last process)을 이용한다.

비아 미들 공정은 BEOL(Back end of line, 웨이퍼에 각종 회로를 새긴 후 반도체 기기를 외부에 연결하기 위한 배선, 보호층을 만드는 공정. 반도체 제조 공정 중 후공정에 속한다)이라 불리는 배선 공정 도중에 via를 만드는 방식이다. via를 만들기 위해 전공정(前工程)에 속하는 웨이퍼 공정을 이용하기 때문에 파운드리처럼 전공정 회사가 주로 사용하는 방법이다.

반면, 비아 라스트 공정은 FEOL(Front-end-of-line, 웨어퍼에 실제 반도체 트랜지스터를 형성하는 공정으로 전공정을 뜻한다)과 BEOL의 모든 배선이 끝난 웨이퍼의 실리콘 기판을 얇게 만든 후 via를 만드는 방식이다. 완성한 웨이퍼를 얇게 만들고 via를 만들어야 하므로 주로 반도체를 조립하거나 테스트를 전문으로 하는, OSAT(Outsourced Semiconductor Assembly and Test)라 불리는 후공정(後工程) 전문 회사가 사용한다.