HBM 고성능화를 위한 핵심 기술, 2.5차원 패키징 기술

지난 기사, ‘HBM을 위한 핵심 반도체 기술, 3차원 집적 기술’에서는 HMB과 같은 첨단 반도체가 탄생하기 위해서는 매우 많은, 그리고 혁신적인 기술이 투입되는데 반도체 성능을 크게 좌우하는 공정 미세화 기술과 3차원 집적 기술에 사람들이 주목하고 있다는 내용과 함께 그중 3차원 집적 기술에 대해 간단하게나마 살펴보는 시간을 가졌다.

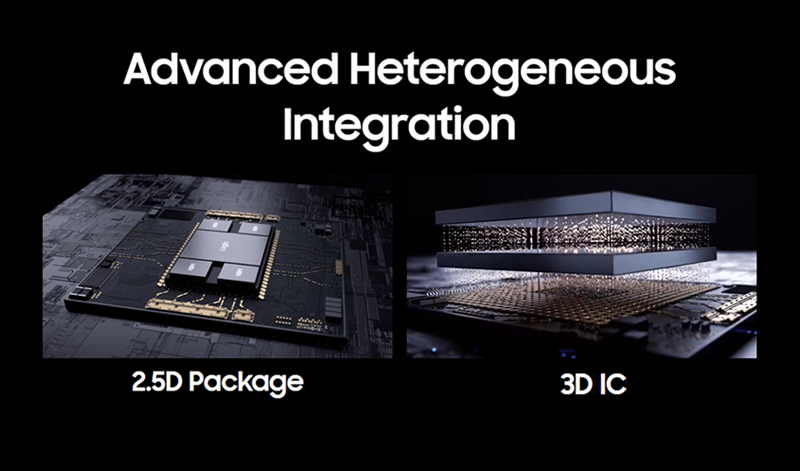

이번 기사에서는 3차원 집적 기술과 연계되면서 첨단 반도체에 적용되는 또 다른 혁신적인 기술 중 하나인 2.5차원 패키징 기술에 대해서 살펴보려 한다. 2.5차원 패키징 기술은 3차원 집적 기술의 구성 요소라 생각하면 이해에 도움이 될 것이다.

네 줄 요약

- 미세화 공정에 의한 반도체 성능 향상이 어려워지면서 2.5차원 패키징 기술이 유력한 대안 중 하나로 꼽히고 있다.

- 여러 반도체 칩을 1개의 패키지 안에 담음으로써 시스템화하는 이종 집적화 기술은 첨단 반도체에 주로 사용된다.

- 2.5차원 패키징 기술은 인터포저 기판 위에 여러 실리콘 다이를 옆으로 나란히 붙여 칩을 탑재하는 기술이다.

- 2.5차원 패키징 기술에 있어 공정 비용 절감과 패키징 면적 최소화는 계속해서 연구, 개발해야 하는 분야다.

2.5차원 패키징 기술은 왜 등장했나?

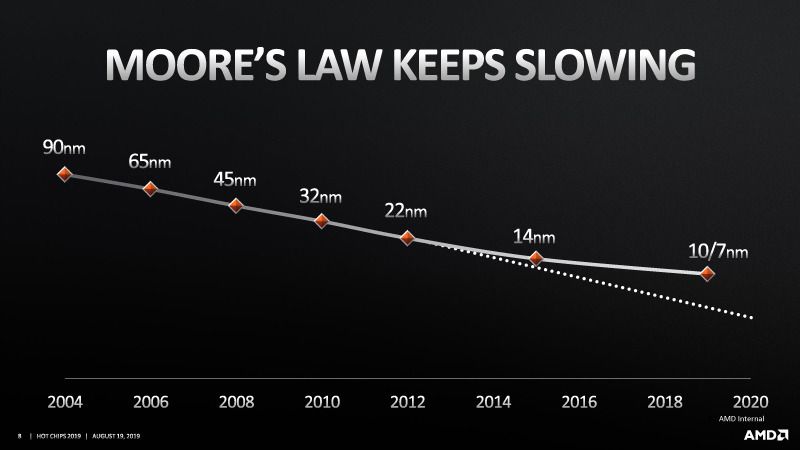

트랜지스터가 탄생한 이후 지금에 이르기까지 반도체 성장을 이끌어온 기본 원리는 반도체 성능은 칩이라는 한정된 공간 안에 얼마나 많은 트랜지스터를 넣느냐에 따라 결정된다는 것이다. 기술 발달에 따라 넣을 수 있는 트랜지스터의 수는 급격히 늘어났고, 이에 따라 반도체 성능도 높아지면서 ‘2년마다 반도체 칩 1개에 탑재되는 트랜지스터가 2배씩 늘어날 것이다’, 즉 반도체 집적도가 2년마다 2배씩 높아질 것이라고 예상한 ‘무어의 법칙’이 탄생하기도 했다(주기와 성능 향상 정도는 여러 사람에 의해 조금씩 수정되어 알려져 왔는데, 무어 본인이 직접 언급한 건 2년마다 2배가 맞다).

무어의 법칙에 따라 시스템의 생산단가는 크게 줄어들고, 동작 주파수 등 반도체 성능은 빠르게 높아졌다. 그리고 기술적으로는 1개의 칩에 많은 기능을 탑재하는, SoC(System on a Chip)로 대표되는 모놀리식(monolithic) IC화 기술(SoC처럼 여러 기능을 갖춘 반도체 IC를 1개의 칩에 담는 전자회로 기술)도 빠르게 발전하고 있다.

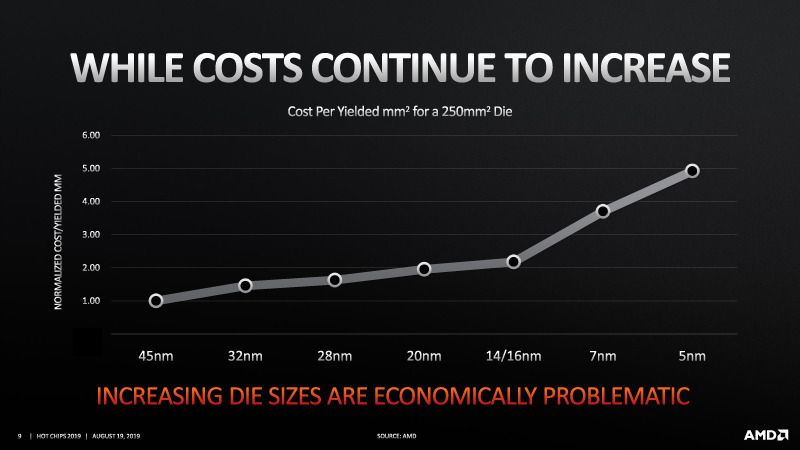

그러나 네트워크와 빅데이터, 그리고 최근에는 AI 관련 기술들이 등장하면서 요구되는 컴퓨팅 성능은 계속해서 높아지고 있지만, 반도체 발전 속도는 이를 따라가지 못하면서 사실상 무어의 법칙은 무용지물이 됐다. 즉, 한계에 달한 미세화 공정으로 인해 반도체 칩 1개당 생산단가는 계속해서 늘어남에 따라 칩 하나에 트랜지스터를 무작정 집적하는 건 의미가 없어진 것이다.

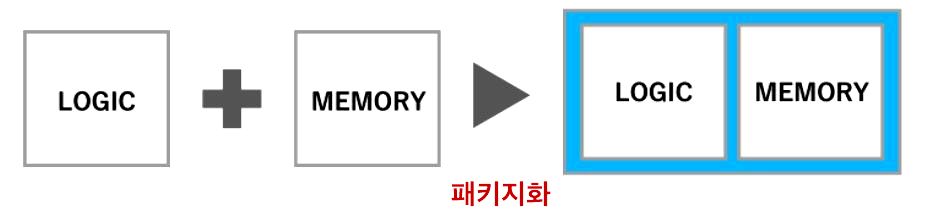

그래서 무어의 법칙을 다시 실현하기 위해, 정확히는 집적도를 높여 생산단가를 줄이기는 어려워졌으니 다른 방법을 통해 생산단가를 줄이는 우회적인 접근이 시도되고 있는데, 이 중 여러 반도체 칩을 하나의 패키지에 담는 방법이 대안으로 떠오르고 있다.

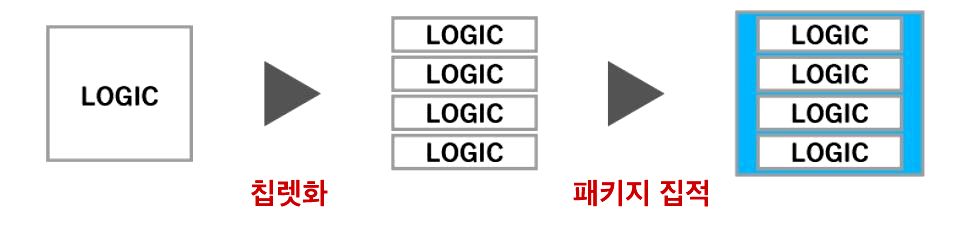

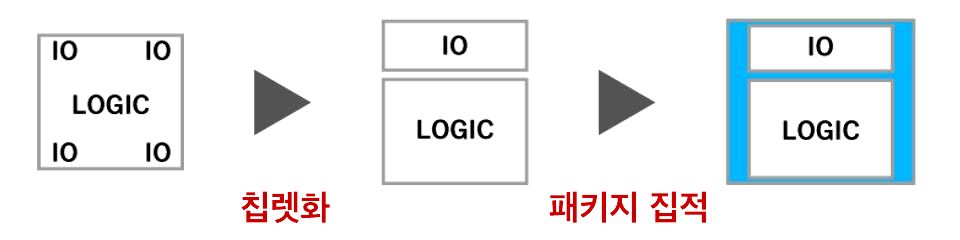

여러 반도체 칩을 하나의 패키지에 담을 때 칩의 기능을 나눠서 패키지에 집적하는 방법, 칩 기능을 정리하고 통합해 패키지에 집적하는 방법 등 여러 방법이 사용되고 있는데, 최근 주목받고 있는 건 칩렛(chiplet)이라 불리는, 모놀리식화되지 않은 여러 반도체 칩을 1개의 패키지 안에 담음으로써 시스템화하는 새로운 패키징 기술, 이종 집적화(異種集積化, Heterogeneous Integration) 기술이다. 이종 집적화 기술은 스마트폰, 고성능 컴퓨터를 비롯한 첨단 반도체에 활발히 채용되고 있다.

2.5차원 패키징의 필요 기술

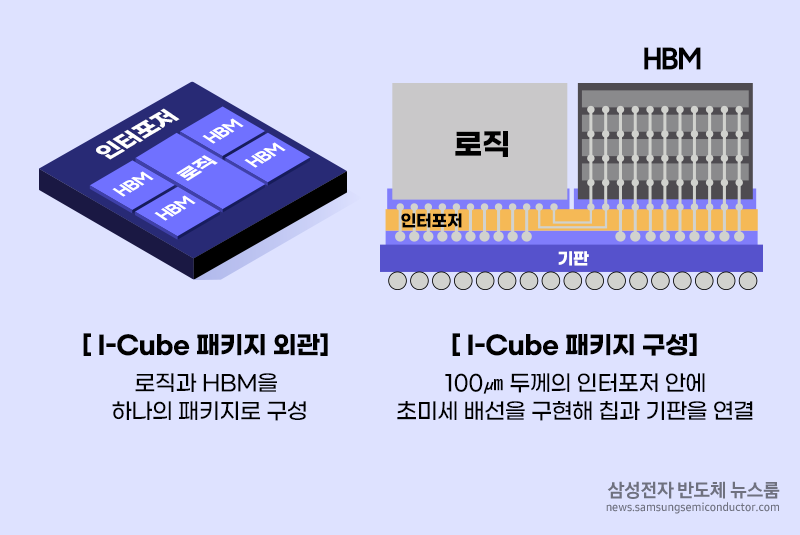

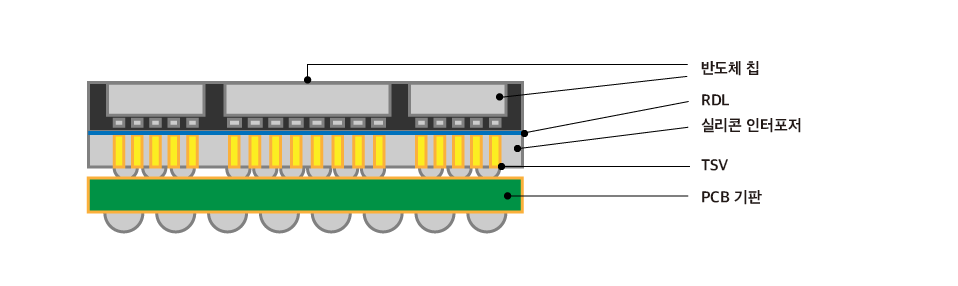

최첨단 패키징 기술을 위해선 크기를 단일 칩 수준으로 작게 만드는 기술과 함께 소비 전력을 줄이는 기술이 갖춰져야 한다. 그래야 성능을 높이는 동시에 많은 기능을 담을 수 있기 때문이다. 이를 해결하기 위해 인터포저 기판 위에 여러 실리콘 다이를 옆으로 나란히 붙여 칩을 탑재하는 2.5차원 패키징 기술이 등장했다.

참고로 인터포저는 패키지 기판(수지 소재)과 실리콘 다이 사이에 있는 중간 기판을 말하는데, 인터포저를 통해 실리콘 다이는 전기적으로 연결된다. 보통 Si 소재가 고성능 반도체용 인터포저로 사용된다.

실리콘 인터포저 윗면에는 여러 층으로 배선된 RDL(Redistribution layer) 회로가 자리해 있고, 이 RDL 회로가 각 칩과 외부 기판을 전기적으로 연결하고, TSV(Through-silicon via, 실리콘 관통 전극)에 의해 아래쪽 수지 기판과 연결된다.

고성능 반도체에서 실리콘 인터포저가 사용되는 이유는 SoC와 비슷한 성능을 패키지상에서 재현하기 위해서는 칩 사이의 거리를 최대한 좁혀 배치할 필요가 있는데, 수지 기판에서는 어려운 RDL 미세 배선이 실리콘에서는 가능하기 때문이다. 그리고 실리콘 기판 위에 실리콘 다이를 올리므로 열팽창계수 차이로 인해 발생하는 웨이퍼 휨 현상을 방지할 수 있는 점도 큰 장점이다. 이로 인해 여러 칩을 인터포저 위에 탑재할 수 있기 때문이다.

증가하는 비용과 면적 해결이 관건

HBM 고성능화를 위한 핵심 기술이자 첨단 도체 고성능화의 핵심으로 꼽히는 2.5차원 패키징 기술이지만, 당면한 문제점도 있다. 비용이 많이 들고, 옆으로 칩을 붙이기 때문에 면적을 많이 차지하게 된다. 면적을 차지한다는 말은 칩의 크기가 커진다는 뜻이고, 이는 고성능화에 걸림돌로 작용한다.

최신 실리콘 인터포저의 크기는 약 3400㎟ 정도로 알려져 있는데, 이 작은 면적에 미세한 돌기(범프)를 만들어 실리콘 다이와 인터포저를 연결하고 정교한 배선을 새기는 공정의 비용도 부담되는 부분이다. 게다가 이 비용은 계속해서 증가하고 있다. 실리콘 인터포저를 만드는 재료비 역시 추가로 들어간다.

그나마 다행인 건 비용을 낮추기 위해서 인터포저 재료로 실리콘을 사용하지 않고 수지를 사용하는 등 새로운 기술이 계속 등장하고 또 발전해나가고 있다는 점이다. 그리고 2.5차원 패키징 기술에 3차원 집적 기술을 도입함으로써 차지하는 면적을 줄이는 기술도 적극적으로 채용되고 있다.

지금은 고성능 컴퓨팅(HPC)이나 스마트폰에 2.5차원 패키징 기술이 주로 사용되고 있지만, 앞으로는 에지 컴퓨팅 용도로도 수요가 늘어날 것이라 예상되기 때문에 패키징 면적 최소화와 공정 비용 절감과 관련한 연구, 개발은 계속 이어질 것이다.